Исследование регистров, счетчиков и дешифраторов (Лабораторная работа)

Цель работы:

исследовать регистры, счетчики и дешифраторы.

Теория

1. Триггеры

Триггерами называются устройства, обладающие двумя устойчивыми

состояниями (Q = 1 и Q = 0) и способные находиться в одном

из них сколь угодно долго и переходить из одного состояния в другое под

воздействием внешних сигналов. В каком из этих состояний окажется триггер,

зависит от сигналов на входах триггера и от его предыдущего состояния, т.е. он

имеет память. Таким образом, триггер – элементарная ячейка памяти.

Тип триггера определяется алгоритмом его работы, в зависимости

от которого триггер может иметь установочные, информационные и управляющие

входы. Установочные входы обуславливают состояние триггера независимо от

состояния других входов. Входы управления разрешают запись данных, подающихся

на информационные входы. Наиболее распространенными являются триггеры RS-, JK-, D- и T-типов.

RS-триггер – простейший автомат с

памятью, который может находиться в двух состояниях. Триггер имеет два

установочных входа: установки S (set –

установка) и сброса R (reset –

сброс), на которые подаются входные сигналы от внешних источников. При подаче

на установки активного логического уровня триггер устанавливается в единицу (Q = 1, Q′ = 0, здесь штрих

означает инвертирование), при подаче активного уровня на вход сброса триггер

устанавливается в ноль (Q = 0, Q′ = 1).

Если на оба установочных входа подать пассивный логический уровень, то триггер

сохраняет предыдущее состояние выходов: Q =

1 или Q = 0. Каждое состояние устойчиво и

поддерживается за счет действия обратных связей. Подача активного уровня

одновременно на оба установочных входа запрещена, так как триггер не может быть

установлен в ноль и единицу.

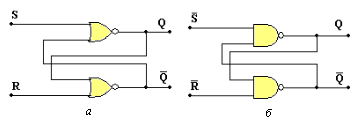

RS-триггер может быть выполнен на

элементах «ИЛИ-НЕ» или «И-НЕ».

Рис. RS-триггер:

а – на элементах «ИЛИ-НЕ», б –

на элементах «И-НЕ»

Для RS-триггеров, выполненных

на элементах «ИЛИ-НЕ», активным уровнем на управляющих входах является уровень

логической единицы, а на элементах «И-НЕ» – уровень логического нуля.

RS-триггер – основной узел

построения последовательных схем. Условия переходов триггеров из одного

состояния в другое можно описать табличным, аналитическим или графическим

способами. Табличное описание работы RS-триггера на элементах

«ИЛИ-НЕ» и «И-НЕ» представлено в табл. 7 и 8 соответственно, где Qt –

предшествующее состояние выхода; Qt+1

– новое состояние, устанавливающееся после перехода; - – неопределенное состояние.

Т а б л и ц а 7 Т а б л и ц а 8

|

R |

S |

Qt+1 |

|

R |

S |

Qt+1 |

|

0 |

0 |

Qt |

|

0 |

0 |

– |

|

1 |

0 |

0 |

|

1 |

0 |

1 |

|

0 |

1 |

1 |

|

0 |

1 |

0 |

|

1 |

1 |

– |

|

1 |

1 |

Qt |

Триггер JK-типа имеет более сложную структуру и более широкие

возможности по сравнению в RS-триггером. Кроме информационных

входов J и K и прямого

и инверсного выходов Q и Q′, JK-триггер имеет вход управления C

(тактирующий или счетный) и два асинхронных установочных входа R и S. Обычно активными уровнями

установочных сигналов являются нули. Установочные входы имеют приоритет над

остальными входами. Активный уровень сигнала на входе S

устанавливает триггер в состояние единица (Q =

1), а на входе R в состояние ноль (Q = 0), независимо от сигналов на

остальных входах. Если на входы установки подать пассивный уровень сигнала, то

состояние триггера будет изменяться по фронту импульса на счетном входе в

зависимости от состояния входов J и K.

Один из вариантов функциональной схемы JK-триггера и его условное графическое изображение, временные диаграммы его работы при R=S=1 приведены ниже.

Рис. JK-триггер:

а – функциональная схема; б

– условное

графическое обозначение

Рис. Временная диаграмма работы JK-триггера

D-триггер имеет один информационный

вход D (data – данные) и один счетный вход C. Информация с входа D записывается в триггер

по положительному перепаду импульса на счетном входе и сохраняется до

следующего положительного перепада. Кроме счетного C и

информационного D входов, у триггера есть два

асинхронных установочных входа R и S. Установочные

входы приоритетные. Активный уровень сигнала на входе S

устанавливает триггер в состояние единица (Q=1), а на входе R в состояние ноль (Q=0), независимо от сигналов на остальных входах.

Условное обозначение D-триггера с диаграммами

входных и выходных сигналов приведено ниже.

Рис. D-триггер: а – условное обозначение; б – временные диаграммы

T-триггер, или счетный триггер, – устройство, осуществляющее счетный режим. Такие

схемы можно построить на основе JK- или D-триггеров.

В D-триггере счетный режим (рис. 30,а) реализуется при помощи обратной

связи, когда на вход D подается сигнал с инверсного

выхода триггера, т.е. всегда осуществляется неравенство сигналов на входе D и на выходе Q (если Q=1, D=0 и

наоборот). Следовательно, при каждом положительном перепаде сигнала на счетном

входе С состояние выхода будет

изменяться на противоположное.

Рис. T-триггер:

а – условное обозначение; б –

временная диаграмма

Таким образом, на каждые два входных тактовых импульса T-триггер формирует один период выходного сигнала Q, т.е. период выходного сигнала в два раза больше периода

входного сигнала. Следовательно, триггер осуществляет деление частоты

fт на его входе на две: fQ

= fт/2, где fQ – частота

следования импульсов на выходе триггера.

2. Регистры

Триггерным регистром называется совокупность триггеров с

определенными связями между ними, при которых они действуют как единое

устройство. Регистры выполняются на синхронных триггерах JK- или D-типа. В зависимости от выполняемых функций регистры делятся

на накопительные (параллельные) и сдвигающие.

В последовательном регистре выход предыдущего триггера

подается на вход следующего триггера, а тактовые импульсы подаются на входы С всех триггеров, составляющих регистр,

одновременно (рис. 31). При этом содержимое каждого триггера записывается в

последующий триггер. Такие регистры называются сдвиговыми регистрами, или

регистрами сдвига.

Рис. Последовательный регистр

(регистр сдвига)

Если на вход D регистра сдвига подать

единицу, а на вход С тактовую

частоту, то единица начнет продвигаться по регистру сдвига, т.е. под воздействием

первого тактового импульса единица запишется в первый триггер регистра. Под

воздействием второго тактового импульса эта единица перепишется во второй

триггер и т.д., когда под воздействием N-го тактового импульса

единица не выйдет из регистра сдвига. Временная диаграмма работы четырехразрядного

регистра сдвига приведена на рис. 32.

Рис. Временная диаграмма четырехразрядного регистра сдвига

Виды регистров сдвига:

1. с

последовательным вводом и выводом;

2. с

последовательным вводом и параллельным выводом;

3. с

параллельным вводом и последовательным выводом;

4. с

переменным направлением сдвига (реверсивные регистры сдвига).

Рис. Параллельный регистр

Кроме последовательных регистров сдвига существуют параллельные

регистры, в

которых информация подается одновременно на все N триггеров

и считывается одновременно с выходов всех триггеров регистра. Тактовая частота

подается одновременно на все триггеры.

Параллельные регистры используются для хранения двоичной

информации небольшого объема в течение короткого промежутка времени.

3.

Счетчики

Счетчиком называется устройство, подсчитывающее число

входных импульсов. Число, представляемое состоянием его выходов по фронту

каждого входного импульса, изменяется на единицу. Счетчик состоит из n последовательно соединенных счетных триггеров, причем выход

одного счетного триггера соединен с тактовым входом следующего триггера.

Счетчики бывают суммирующими (прямой счет) и вычитающими (обратный счет). В

суммирующих счетчиках каждый входной импульс увеличивает число на его выходах

на единицу, в вычитающих счетчиках уменьшает это число на единицу. Для того

чтобы построить суммирующий счетчик, необходимо счетный вход очередного

триггера подключить к инверсному выходу предыдущего (рис. 34).

Рис. Суммирующий счетчик и диаграмма

его работы

Для того чтобы изменить направление счета (реализовать

вычитающий счетчик), необходимо счетный вход очередного триггера подключить к

прямому выходу предыдущего, при этом изменяется последовательность переключения

триггеров.

Рис. Вычитающий счетчик и диаграмма

его работы

Счетчик характеризуется числом состояний в течение одного

периода (цикла). Для двоичных счетчиков полный цикл счета N=2n от состояния 0..000 до состояния 1…11. Число

состояний называется коэффициентом пересчета Kсч,

равным отношению числа импульсов Nс на входе к

числу импульсов NQст на выходе

старшего разряда за период:

![]() .

.

Если на вход счетчика подавать периодическую

последовательность импульсов с частотой fс, то частота

fQ на выходе старшего разряда счетчика будет

меньше в Kсч раз: Kсч= fс/fQ. Поэтому счетчики также называют делителями

частоты, а Kсч – коэффициентом

деления. Для увеличения величины Kсч нужно

увеличить число триггеров в цепочке. Каждый дополнительный триггер удваивает

число состояний счетчика и число Kсч.

4. Дешифраторы

Комбинационной называется логическая схема, реализующая

однозначное соответствие между значениями входных и выходных сигналов.

Дешифратор – логическая комбинационная схема, имеющая n

информационных входов и 2n выходов. Каждой

комбинации логических уровней на входах будет соответствовать активный уровень

на одном из 2n выходов. Как любая

логическая схема, дешифратор может быть задан таблицей истинности. Таблица

истинности дешифратора 3х8 состоит из трех столбцов, соответствующих входным

сигналам Х0, Х1, Х2, и восьми столбцов, соответствующих выходным сигналам

Y0, Y1, Y2, Y3, Y4, Y5, Y6, Y7. В первых

слева трех столбцах расположены возможные комбинации входных сигналов, а в

последних восьми – соответствующие им комбинации выходных сигналов.

Таблица истинности

дешифратора

|

Х2 |

Х1 |

Х0 |

Y7 |

Y6 |

Y5 |

Y4 |

Y3 |

Y2 |

Y1 |

Y0 |

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

|

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

|

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Схема имеет восемь выходов, на одном из которых потенциал

высокий, на остальных низкий. Номер единственного выхода, имеющего высокий

потенциал, соответствует двоичному числу, формируемому состояниями входных

сигналов. Этот принцип формирования выходного сигнала можно описать следующим

образом: Yi = 0, если i = k; Yi

= 1, если i ≠ k, здесь i – номер разряда; k = 22 X2 + 21 X1 + 20X0.

Выражения для каждого выхода дешифратора:

где

«¯» – инвертирование.

Таким образом, схема дешифратора должна содержать три

схемы «НЕ» и восемь схем «3И».

Рис. Схема дешифратора 3х8

Последовательность выполнение работы

Исследование регистра

1. Нарисовать

схему четырехразрядного регистра сдвига с автоматической записью единицы в

первый разряд регистра.

Рис. Четырехразрядный регистр сдвига

с автоматической записью единицы

Схема содержит четыре D-триггера, четыре

светодиода, одну логическую схему «4ИЛИ-НЕ», функциональный генератор и

логический анализатор. Логическая схема «4ИЛИ-НЕ» служит для автоматической

записи единицы в регистр. На выходе этой схемы единица будет только тогда,

когда все разряды регистра будут находиться в нулевом состоянии.

2.

Открыть окно

функционального генератора и установить вид генерируемых сигналов (прямоугольные

импульсы), генерируемую частоту 1000 Гц, амплитуду генерируемых импульсов

5 В.

3. Открыть

окно логического анализатора, дважды щелкнув по иконке логического анализатора.

4. Запустить

процесс моделирования, нажав кнопку ![]() на

панели инструментов, и в появившемся меню выбрать команду Run.

на

панели инструментов, и в появившемся меню выбрать команду Run.

5. Зарисовать

диаграммы сигналов с экрана логического анализатора.

6. Зарисовать

все состояния светодиодов и сравнить их с временными диаграммами.

Описание

используемых контрольно-измерительных приборов

Функциональный

генератор (Function Generator)

На лицевой панели функционального генератора расположены

три кнопки ![]() , с помощью которых выбирается форма

генерируемого сигнала: синусоидальной (выбирается по умолчанию), треугольной и

прямоугольной.

, с помощью которых выбирается форма

генерируемого сигнала: синусоидальной (выбирается по умолчанию), треугольной и

прямоугольной.

Рис. Лицевая панель функционального генератора

В четырех белых окнах устанавливают параметры выходного

сигнала:

1)

частоты –

![]() ,

,

2) коэффициента

заполнения в процентах. Для импульсных сигналов это отношение длительности

импульса к периоду повторения (величина обратная скважности), для треугольных

сигналов – соотношение между длительностями переднего и заднего фронтов – ![]() ,

,

3) амплитуды выходного

сигнала – ![]() ,

,

4)

смещения

(постоянной составляющей) – ![]() .

.

В низу лицевой панели расположены выходные зажимы ![]() ; при заземлении клеммы COM (общий) на клеммах «+» и «-» генератор

выдает парафазный сигнал.

; при заземлении клеммы COM (общий) на клеммах «+» и «-» генератор

выдает парафазный сигнал.

Логический

анализатор (Logic Analyzer)

Логический анализатор предназначен для отображения на экране монитора

16-разрядных кодовых последовательностей одновременно в шестнадцати точках

схемы, а также в виде двоичных чисел на входных клеммах-индикаторах.

Рис. Лицевая панель логического анализатора

Анализатор снабжен двумя визирными линейками для точных отсчетов

временных интервалах Т1, Т2 и Т2

– Т1 (окно в поле Т1, Т2,

Т2-Т1), а также линейкой прокрутки по горизонтали для просмотра

осциллограмм на большом временном интервале.

На панели Clock в строке Clocks/Div задается длительность развертки. В этом блоке имеются

клеммы для подключения как обычного (Extend), так и избирательного (Qualifier) источника запускающих сигналов, параметры которых

устанавливаются с помощью меню, вызываемого кнопкой Set.

В окне Trigger можно задать логические сигналы 1, 0 и Х, при наличии которых производится запуск

анализатора.

Кнопки Stop и Reset предназначены для остановки и перезапуска режима

моделирования.

Исследование

суммирующего счетчика

1.

Нарисовать схему четырехразрядного счетчика,

считающего в прямом направлении (рис. 40).

Рис. 40 . Четырехразрядный

суммирующий счетчик

Поместить на схему четыре D-триггера,

четыре светодиода, функциональный генератор, логический анализатор и 16-ричный

индикатор.

2. Открыть

окно логического анализатора, щелкнув по иконке логического анализатора.

3. Запустить

процесс моделирования, нажав кнопку ![]() на

панели инструментов, и в появившемся меню выбрать команду Run.

на

панели инструментов, и в появившемся меню выбрать команду Run.

4. Зарисовать

диаграммы сигналов с экрана логического анализатора.

5.

Зарисовать все состояния светодиодов и сравнить

их с временными диаграммами.

6.

Наблюдать за показаниями 16-ричного индикатора и

сравнить его показания с соответствующими состояниями светодиодов.

Исследование

вычитающего счетчика

1.

Нарисовать схему четырехразрядного счетчика,

считающего в обратном направлении.

Рис. Четырехразрядный вычитающий счетчик

2. Открыть

окно логического анализатора, щелкнув по иконке логического анализатора.

3. Запустить

процесс моделирования, нажав кнопку ![]() на

панели инструментов, и в появившемся меню выбрать команду Run.

на

панели инструментов, и в появившемся меню выбрать команду Run.

4. Зарисовать

диаграммы сигналов с экрана логического анализатора.

5.

Зарисовать все состояния светодиодов и сравнить

их с временными диаграммами.

6. Наблюдать за показаниями 16-ричного индикатора и

сравнить его показания с соответствующими состояниями светодиодов.

Исследование

дешифратора

1. Нарисовать

схему дешифратора 3х8. Для этого поместить на схему восемь логических схем

«3И», восемь светодиодов, пять логических схем «НЕ», три переключателя на два

направления и три вольтметра.

2. Присвоить

переключателям управляющие клавиши.

3. С

помощью переключателей подать на вход дешифратора все возможные комбинации сигналов

и записать для каждого входного сигнала выходной сигнал (восьмиразрядную комбинацию),

т.е. заполнить таблицу истинности.

Рис. Дешифратор 3х8

Содержание

отчета

Отчет должен включать:

1) название пункта работы,

2) исследуемую схему,

3) результат моделирования. Для регистра и счетчиков

привести временные диаграммы, для дешифратора – таблицу истинности.